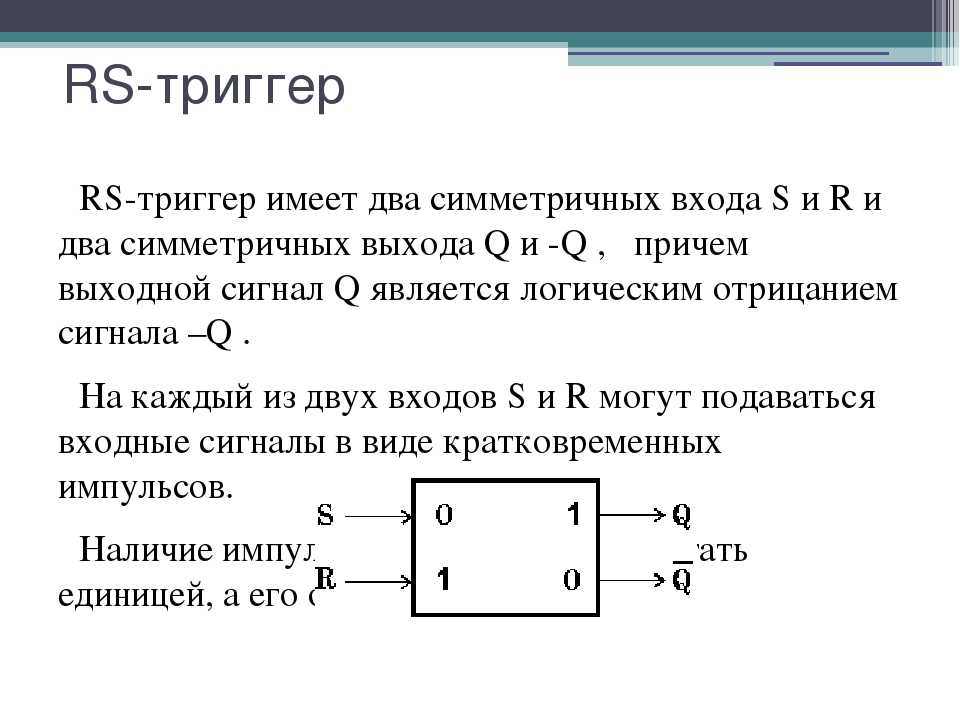

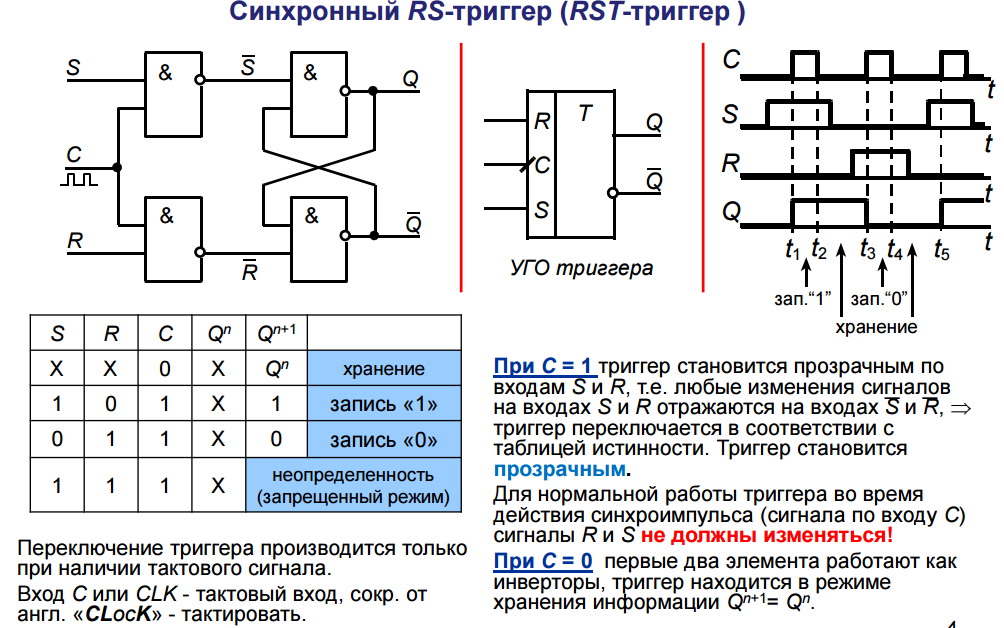

Регистры на триггерах

RS-триггер способен сохранять 1 бит цифровой информации. Если необходимо хранить несколько бит, например, цифровое двоичное слово из нескольких двоичных разрядов (в микроконтроллерах обычно 8 или 16), то триггеры могут соединяться параллельно, образуя регистры. Это простейшие устройства для временного хранения набора двоичных цифровых разрядов, в которых каждый триггер сохраняет значение одного разряда (0 или 1. т. е. один бит). Так, показанный ниже 4-разрядный регистр на RS-триггерах содержит четыре отдельных триггера.

![]()

Любое двоичное число от (0000)2 до (1111)2 может быть сохранено в этом регистре просто путем установки или сброса соответствующего триггера. Давайте предположим, что первый триггер установлен (Q1 = 1), второй сброшен (Q2 = 0), третий также сброшен (Q3 = 0), а четвертый установлен (Q4 = 1). Тогда двоичное число, записанное в регистр, будет (1001)2.

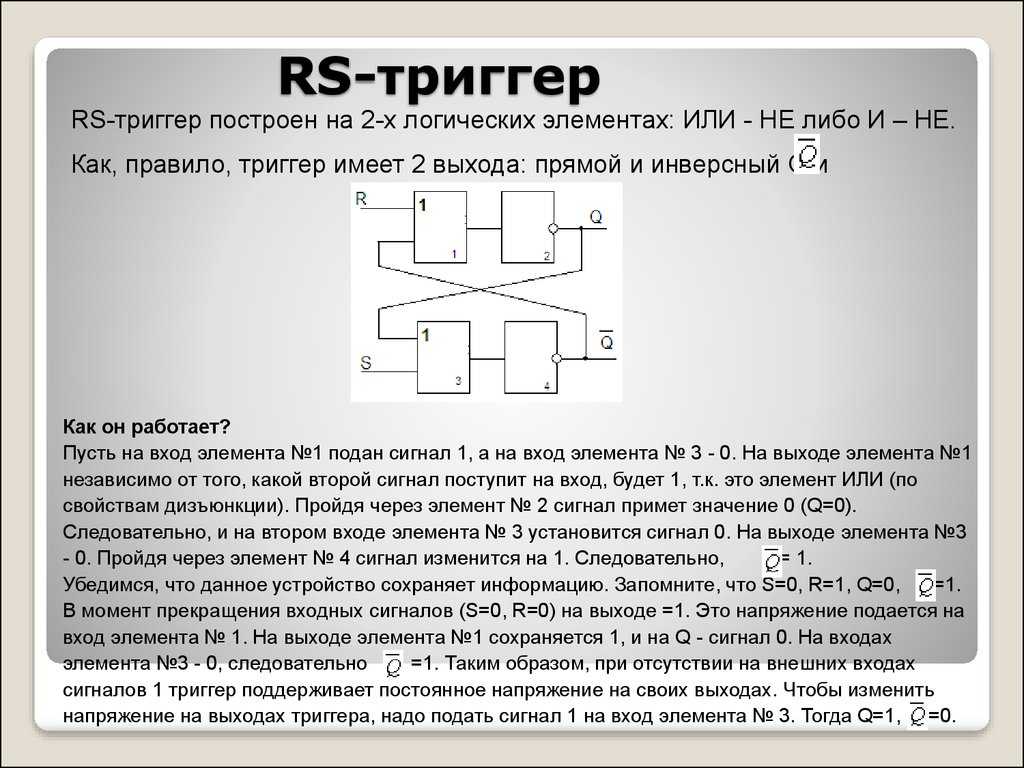

Кроме параллельных регистров, предназначенных для хранения цифровых слов, на RS-триггерах делаются и так называемые регистры сдвига, в которых разряды цифрового слова последовательно с приходом каждого тактового импульса сдвигаются влево или вправо на один разряд. Схема такого устройства на синхронных триггерах показана ниже.

![]()

Подобные регистры находят применение в схемах последовательных интерфейсов, когда поступающие из управляющего контроллера цифровые слова побитно передаются в линию связи.

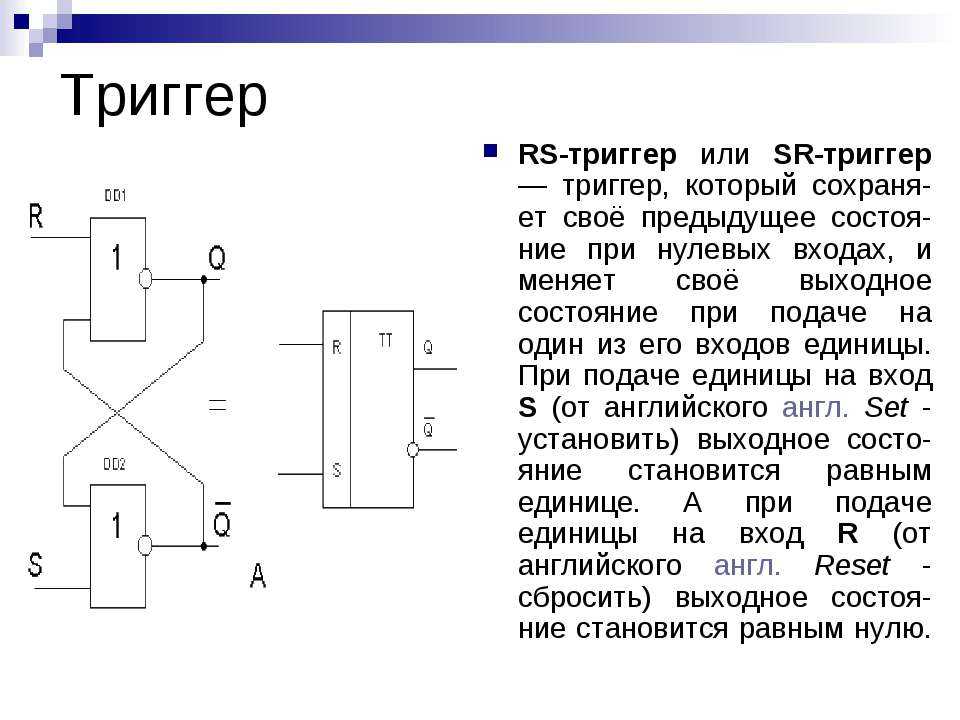

Принцип работы RS триггера

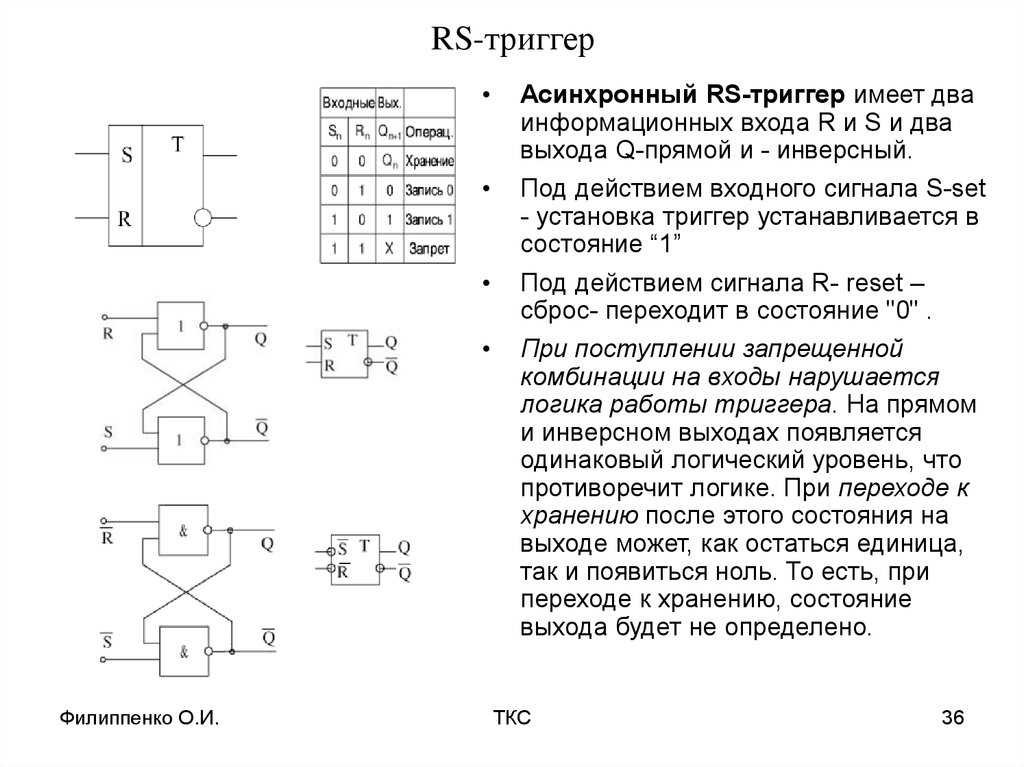

Система, представленная выше, при помощи электромагнитных реле иллюстрирует работу триггера на элементах ИЛИ-НЕ. Однако в современных схемах электромеханические приборы давным-давно не используются, сейчас они собираются из электронных логических элементов на транзисторах, заключенных внутри интегральных микросхем. К тому же для их реализации можно использовать различные базисы. Пример схемы RS триггера на элементах И-НЕ, охваченных положительной обратной связью.

Допустим, что на оба входа R и S подаются единицы. Если верхний элемент И-НЕ выдаст на прямой выход Q логический 0, благодаря положительной обратной связи он поступит на свободный вход нижнего элемента, вследствие чего тот выдаст на инверсном выходе единицу (1). В свою очередь, эта 1 по обратной связи поступает на вход верхнего элемента, тем самым подтверждая 0 на выходе Q. Если же на прямом выходе изначально находится 1, то инверсный, соответственно, выдаст 0, который подтвердит 1 на выходе Q.

![]()

Транзисторная схема RS триггера

При подаче на S-вход 0, согласно логической функции И-НЕ, на прямом выходе Q возникнет 1, а на инверсном – 0. Если при этом на вход S снова подать 1, состояние триггера не изменится, так как по таблице истинности И-НЕ при подаче на входы элемента комбинации 0 и 1 либо 0 и 0, на выходе всегда будет 1. Таким образом, триггерная схема сохраняет полученное значение неизменным. Сбросить значение Q обратно в 0 можно, только подав сигнал на сбрасывающий вход R. Практически работу RS триггера можно пронаблюдать, собрав такую схему на транзисторах.

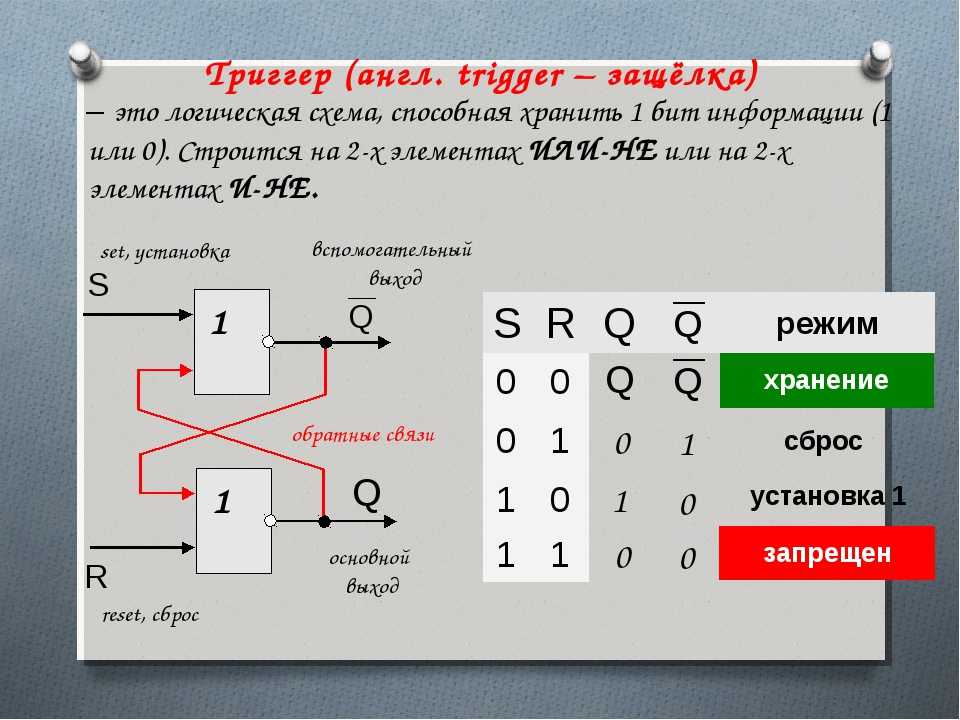

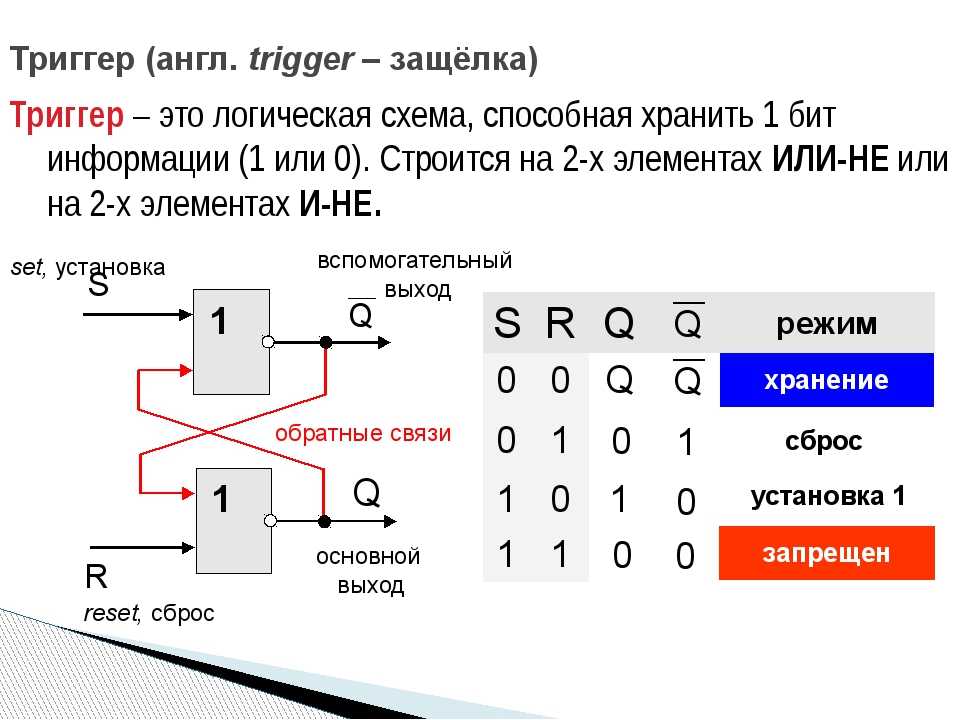

Что такое триггер?

![]()

Триггерами называют целый класс электронных устройств, которые имеют такое свойство, как длительное нахождение в одном из двух устойчивых состояний. Чередование осуществляется под воздействием внешних сигналов. Текущее состояние триггера с легкостью распознаётся благодаря наличию выходного напряжения. Отличительной способностью всего класса является свойство запоминать двоичную информацию. Тут возникает вопрос: есть ли у триггеров память? В обычном понимании нет. Но, тем не менее, они остаются в одном из 2 состояний, причем и после прекращения подачи сигнала. Благодаря этой особенности и считается, что они могут запоминать двоичную информацию.

При изготовлении триггеров на данный момент применяют полупроводниковые приборы (обычно полевые и биполярные транзисторы). Раньше использовали электронные лампы и электромагнитные реле. Своё применение триггеры нашли в интеграционных средах разработки, которые создаются для различных программируемых логических интегральных схем. Если говорить конкретнее, то их используют, чтобы организовать компоненты вычислительных систем: счетчики, регистры, процессоры и ОЗУ.

RS-триггеры

RS-триггер получил название по названию своих входов. Вход S

(Set — установить англ.) позволяет устанавливать выход Q в единичное состояние. (Устанавливать означает

записывать логическую единицу). Вход R (Reset — сбросить англ.) позволяет сбрасывать выход Q

(Quit — выход англ.) в нулевое состояние.

Для реализации RS-триггера воспользуемся логическими элементами «2И-НЕ». Его

принципиальная схема, реализованная на логических элементах «2И-НЕ»,

приведена на рисунке 2.

Рассмотрим работу изображенной на рисунке 2 схемы триггера подробнее. Пусть на входы R и S подаются

единичные потенциалы. Если на выходе верхнего логического элемента «2И-НЕ» Q присутствует логический ноль, то на

выходе нижнего логического элемента «2И-НЕ» появится логическая единица. Эта единица подтвердит логический ноль на

выходе триггера Q. Если на выходе верхнего логического элемента «2И-НЕ» Q первоначально присутствует логическая

единица, то на выходе нижнего логического элемента «2И-НЕ» появится логический ноль. Этот ноль подтвердит логическую

единицу на выходе Q. То есть, при единичных уровнях на входах R и S, схема RS-триггера работает точно так же,

как и схема триггера на инверторах.

Подадим на вход S триггера нулевой потенциал. Согласно таблице истинности логического элемента «2И-НЕ» на выходе Q

появится единичный потенциал. Это приведёт к появлению на инверсном выходе триггера нулевого потенциала. Теперь, даже

если снять нулевой потенциал с входа S, на выходе триггера останется единичный потенциал. То есть мы записали в триггер

логическую единицу.

Точно так же можно записать в триггер и логический ноль. Для этого следует воспользоваться входом R. Так как активный

уровень на входах триггера оказался нулевым, то эти входы — инверсные. Составим таблицу истинности RS-триггера.

Входы R и S в этой таблице будем использовать прямые, то есть запись нуля, и запись единицы будут осуществляться

единичными потенциалами (таблица 1).

| R | S | Q(t) | Q(t+1) | Пояснения |

| Режим хранения информации (триггером) R=S=0 | ||||

| 1 | 1 | |||

| 1 | 1 | Режим установки триггера в единичное состояние S=1 | ||

| 1 | 1 | 1 | ||

| 1 | Режим записи нуля в триггер R=1 | |||

| 1 | 1 | |||

| 1 | 1 | * | R=S=1 запрещенная комбинация | |

| 1 | 1 | 1 | * |

RS-триггер можно построить и на логических элементах «2ИЛИ-НЕ». Схема RS-триггера, построенного на

логических элементах «2ИЛИ-НЕ» приведена на рисунке 3. Единственное отличие в работе этой схемы

триггера будет заключаться в том, что его сброс и установка будет производиться единичными логическими уровнями.

Эти особенности реализации схемы триггера связаны с принципами работы инверсной логики, которые рассматривались

ранее.

Так как RS-триггер при построении его на логических элементах «2И-НЕ» и «2ИЛИ-НЕ» работает одинаково, то его

условно-графическое изображение на принципиальных схемах тоже одинаково. Условно-графическое изображение RS-триггера

на принципиальных схемах приведено на рисунке 4.

Для измерения логических уровней на выходе триггера чаще всего применяются логические пробники, в качестве

которых в простейшем случае можно использовать светодиод с токоограничивающим резистором. В качестве источника

логического сигнала можно применить механические тумблеры.

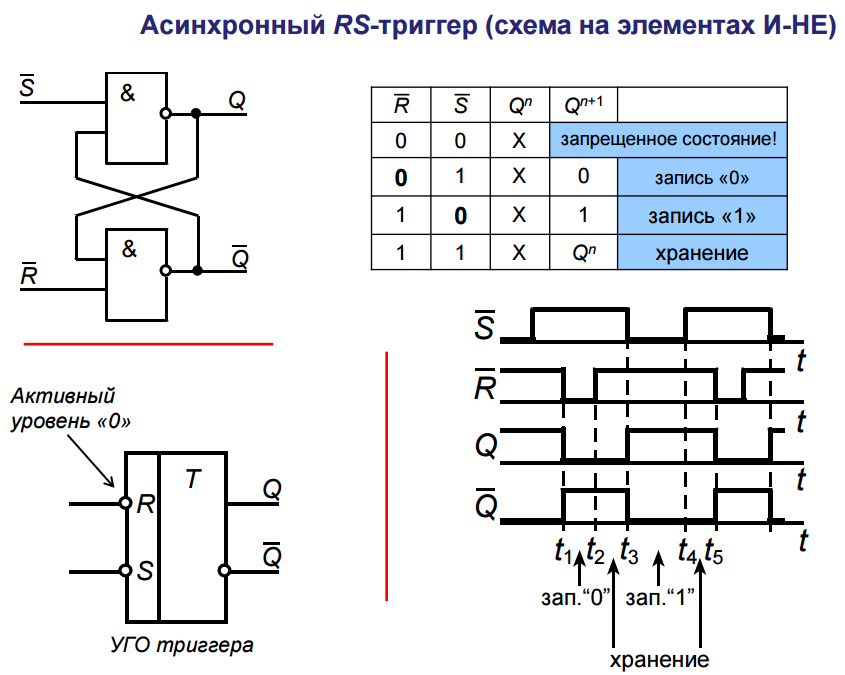

RS-триггер.

Асинхронный

триггер RS-типа (рис 1) имеет два информационных входа R и S. Входы S и R

названы по первым буквам английских слов set — установка и reset — сброс. При

S=1 и R=0 на выходах триггера появляются сигналы: на прямом выходе Q=1, на

инверсном Q=0. При S=0 и R=1 выходные сигналы триггера принимают

противоположные состояния (Q=0, Q=1). Этот триггер не имеет тактового

входа.

Простейший RS-триггер можно реализовать

на логических элементах

ИЛИ-НЕ или И-НЕ, как показано на рисунке 1.

![]()

Рис. 1.Асинхронный RS-триггер на логических элементахИЛИ-НЕ и И-НЕ.

Проиллюстрировать работу такого

асинхронного триггера можно с помощью таблиц истинности или временных диаграмм

(рис.2)

Обратите внимание, что простейший триггер при S=1 и R=0 устанавливается в состояние

логического нуля (и наоборот). Здесь Q – состояние выхода до установки

входных сигналов (режим хранения)

|

На элементах ИЛИ-НЕ |

На элементах И-НЕ |

||||||

|

Вход S |

Вход R |

Прям. Q |

Инвер. Q |

Вход S |

Вход R |

Прям. Q |

Инвер. Q |

|

Q |

Q |

1 |

1 |

||||

|

1 |

1 |

1 |

1 |

1 |

|||

|

1 |

1 |

1 |

|||||

|

1 |

1 |

1 |

1 |

Q |

Q |

При одновременном

поступлении сигнала 1 или 0 на входы R и S выходные сигналы триггера не определены,

поэтому в устройствах на основе RS-триггера необходимо исключать такие режимы (запрещенное состояние). Существуют

разновидности RS-триггера, носящие название Е-, R- и S-триггеров, для которых сочетание

S=1 и R=1 не является запрещенным.

Рис. 2.Синхронный RS-триггер. Справа – его временные диаграммы.

Синхронный одноступенчатый RS-триггер рис. 2 отличается от асинхронного наличием

С-входа для синхронизирующих тактовых импульсов. Синхронный триггер состоит из

асинхронного RS-триггера и двух логических элементов на его входе.

Переключение

этого триггера происходит только при появлении высокого уровня на тактовом

входе С, что хорошо видно на временной диаграмме, рис. 2.

Триггер RS

используется как устройство памяти в других типах триггеров.

Регистры на триггерах

Так как один переключатель является однобитовой ячейкой памяти, то, чтобы сохранить несколько бит, нужно увеличить количество единичных хранилищ. Цепочка из таких ячеек носит названия регистра. Регистр позволяет временно хранить цифровые данные двоичных разрядов. Количество разрядов зависит от количества однобитовых ячеек.

![]() Схема 4-х разрядного регистра сдвига на триггерах

Схема 4-х разрядного регистра сдвига на триггерах

Использование элементарных электронных цифровых устройств – триггеров, позволяет составлять сложные схемы управления логическими устройствами. Одна элементарная защёлка памяти своим бистабильным состоянием помогает осуществлять самые сложные схемные решения.

Краткие теоретические сведения

Триггеры предназначены для запоминания двоичной информации. Использование триггеров позволяет реализовывать устройства оперативной памяти (то есть памяти, информация в которой хранится только на время вычислений).

Однако триггеры могут использоваться и для построения некоторых цифровых устройств с памятью, таких как счётчики, преобразователи последовательного кода в параллельный или цифровые линии задержки.

RS-триггер

Основным триггером, на котором базируются все остальные триггеры является RS-триггер. RS-триггер имеет два логических входа:

- R – установка 0 (от слова reset);

- S – установка 1 (от слова set).

RS-триггер имеет два выхода:

- Q – прямой;

- Q- обратный (инверсный).

Состояние триггера определяется состоянием прямого выхода. Простейший RS-триггер состоит из двух логических элементов, охваченных перекрёстной положительной обратной связью.

Рассмотрим работу триггера:

Пусть R=0, S=1. Нижний логический элемент выполняет логическую функцию ИЛИ-НЕ, т.е. 1 на любом его входе приводит к тому, что на его выходе будет логический ноль Q=0. На выходе Q будет 1 (Q=1), т.к. на оба входа верхнего элемента поданы нули (один ноль – со входа R, другой – с выхода ). Триггер находится в единичном состоянии. Если теперь убрать сигнал установки (R=0, S=0), на выходе ситуация не изменится, т.к. несмотря на то, что на нижний вход нижнего логического элемента будет поступать 0, на его верхний вход поступает 1 с выхода верхнего логического элемента.

https://youtube.com/watch?v=6lT1TH7nglo

Триггер будет находиться в единичном состоянии, пока на вход R не поступит сигнал сброса. Пусть теперь R=1, S=0. Тогда Q=0, а =1. Триггер переключился в “0”. Если после этого убрать сигнал сброса (R=0, S=0), то все равно триггер не изменит своего состояния. Для описания работы триггера используют таблицу состояний (переходов). Обозначим:

- Q(t) – состояние триггера до поступления управляющих сигналов (изменения на входах R и S);

- Q(t+1) – состояние триггера после изменения на входах R и S.

Таблица переходов RS триггера в базисе ИЛИ-НЕ

| R | S | Q(t) | Q(t+1) | Пояснения |

| Режим хранения информации R=S=0 | ||||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S=1 | ||

| 1 | 1 | 1 | ||

| 1 | Режим установки нуля R=1 | |||

| 1 | 1 | |||

| 1 | 1 | * | R=S=1 запрещённая комбинация | |

| 1 | 1 | 1 | * |

RS-триггер можно построить и на элементах “И-НЕ” (рисунок 2.2).

Входы R и S инверсные (активный уровень “0”). Переход (переключение) этого триггера из одного состояния в другое происходит при установке на одном из входов “0”. Комбинация R=S=0 является запрещённой.

Таблица переходов RS триггера в базисе “2И-НЕ”

| R | S | Q(t) | Q(t+1) | Пояснения |

| * | R=S=0 запрещённая комбинация | |||

| 1 | * | |||

| 1 | Режим установки нуля R=0 | |||

| 1 | 1 | |||

| 1 | 1 | Режим установки единицы S=0 | ||

| 1 | 1 | 1 | ||

| 1 | 1 | Режим хранения информации R=S=1 | ||

| 1 | 1 | 1 | 1 |

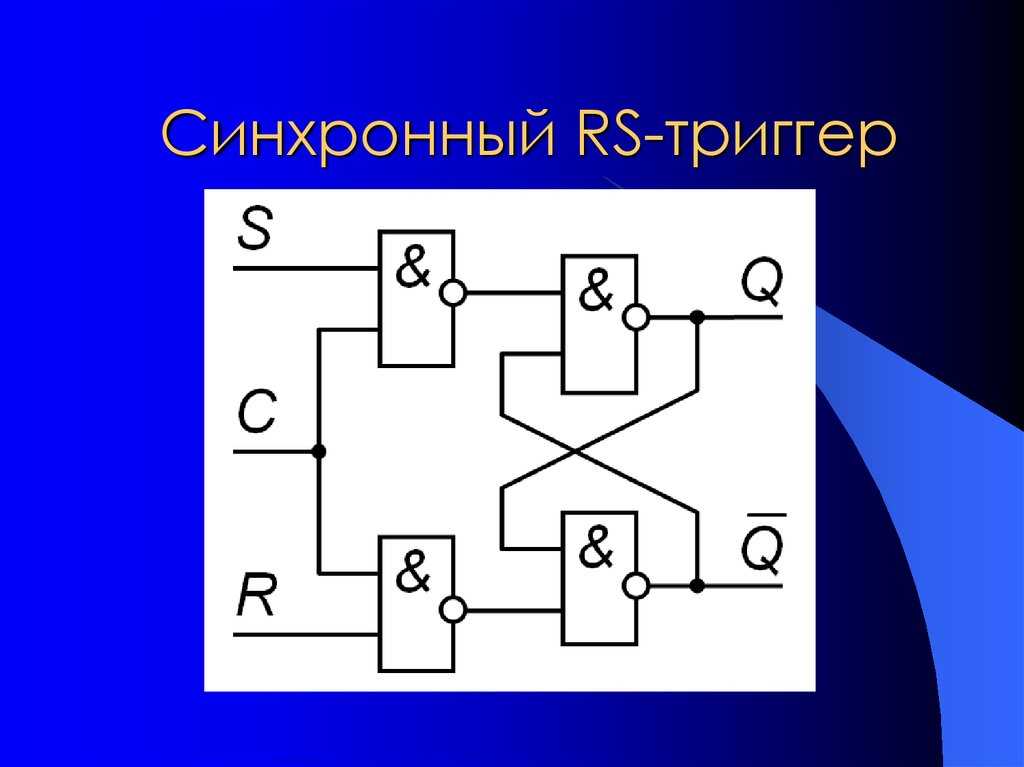

Синхронный RS-триггер

Схема RS-триггера позволяет запоминать состояние логической схемы, но так как при изменении входных сигналов может возникать переходный процесс (в цифровых схемах этот процесс называется “опасные гонки”), то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены, и сигнал на выходе комбинационной схемы соответствует выполняемой ею функции. Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала).

Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Триггеры, запоминающие входные сигналы только в момент времени, определяемый сигналом синхронизации, называются синхронными. Принципиальная схема синхронного RS триггера приведена.

Таблица переходов синхронного RS-триггера

| R | S | C | Q(t) | Q(t+1) | Пояснения |

| 1 | Режим хранения информации R = S = 0 | ||||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | Режим установки единицы S =1 | ||

| 1 | 1 | 1 | 1 | ||

| 1 | 1 | Режим установки нуля R=1 | |||

| 1 | 1 | 1 | |||

| 1 | 1 | 1 | * | R = S = 1 запрещённая комбинация | |

| 1 | 1 | 1 | 1 | * |

В таблице 2.3. под сигналом С подразумевается синхроимпульс. Без синхроимпульса синхронный RS триггер сохраняет своё состояние.

Описание и принцип работы

В широком смысле триггером (от английского trigger — спусковой крючок, запускающий механизм) называют любой импульс или событие, ставшее причиной чего-либо. Термин применяют в электронике, психологии, медицине, программировании и других областях деятельности. В создании микросхем и других устройств так называют элемент, который способен принимать одно из двух стойких состояний (0 или 1) и сохранять их в течение долгого времени.

Положение триггера зависит от получаемых им сигналов на прямом и инверсном выходах. Отличительной чертой устройства является то, что его переход из одной позиции в другую обусловлен не только получением внешних инструкций, поступающих от выбранной системы управления, но и посредством обратной связи. То есть текущее положение элемента зависит от предыстории его работы.

Триггеры могут сохранять свою память только при постоянном поступлении напряжения. Если его отключить, а затем снова подключить, устройство перейдёт в случайное состояние

Поэтому при конструировании устройства важно предусмотреть способ, которым он изначально будет вводиться в правильное положение

В основе любого триггера лежит схема, которая состоит из двух логических элементов типа И-НЕ либо ИЛИ-НЕ, имеющих друг с другом обратную положительную связь. Такой тип подключения позволяет системе иметь всего два возможных устойчивых состояния, из которых выбирается одно

Важной деталью является то, что после того как триггер перешёл в положение, он может сохранять его сколько угодно времени, до тех пор, пока не будет подан очередной управляющий сигнал

Другой характерной особенностью устройств является возможность мгновенного осуществления перехода от одного состояния в другое после получения соответствующей команды. Задержка настолько мала, что её можно не учитывать при проведении расчётов.

Число входов может быть разным и зависит от требуемых функций. Если подать сигнал одновременно на два из них, то он примет произвольную позицию после прекращения их поступления. По своим функциям входы делятся на несколько типов, которые входят в две большие группы: информационные и управляющие. Первые из них получают сигналы и запоминают их в виде информации, в то время как вторые разрешают или запрещают её запись, а также выполняют функцию синхронизации. На схемах они имеют следующие обозначения:

- S — устанавливает триггер в состояние «1» на прямом выходе;

- R — противоположен S, сбрасывает состояние обратно на «0»;

- С — вход синхронизации;

- D — принимает информацию для последующего занесения на триггер;

- T — счётный вход.

https://youtube.com/watch?v=RRYecDSzxHY

Классификация

Если стандартные логические элементы являются строительными блоками комбинационных схем, бистабильные схемы, включая и RS-триггер, являются основными компонентами построения последовательностных логических устройств, таких, как регистры хранения данных, регистры сдвига, устройства памяти или счетчики. В любом случае рассматриваемые триггеры (разумеется, как и все последовательностные схемы) могут быть выполнены в виде следующих основных типов:

1. Асинхронный RS-триггер – схема, которая изменяет состояние сразу при изменении входных сигналов. Для рассматриваемого типа устройств ими являются сигналы на информационных входах R (сброс) и S (установка). Согласно установившейся практике, соответствующие входы называют так же, как и сигналы на них.

2. Синхронный RS-триггер, управляемый статически, работа которого синхронизирована с уровнем определенного тактового сигнала.

3. Триггер по п.2 с динамическим управлением, работа которого синхронизирована с моментами появления фронтов (или спадов) тактового сигнала.

Таким образом, если изменения состояния выходов происходят только при наличии тактового сигнала, который подается на отдельный тактовый вход C, то триггер является синхронным. В противном случае схема считается асинхронной. Чтобы сохранить свое текущее состояние, последовательностные схемы используют обратную связь, т. е. передачу части выходного сигнала на ее вход.

D триггеры, работающие по фронту.

Фронт сигнала синхронизации, в отличие от высокого (или низкого) потенциала, не может длиться продолжительное время.

В идеале длительность фронта равна нулю. Поэтому в триггере, запоминающем входную информацию по фронту не нужно предъявлять

требования к длительности тактового сигнала.

Триггер, запоминающий входную информацию по фронту, может быть построен из двух триггеров, работающих по потенциалу.

Сигнал синхронизации будем подавать на эти триггеры в противофазе. Схема такого триггера приведена на рисунке 15.

Рассмотрим работу схемы динамического триггера, приведенной на рисунке 15 подробнее. Для этого воспользуемся

временными диаграммами, показанными на рисунке 13. На этих временных диаграммах обозначение Q΄ соответствует

сигналу на выходе первого триггера. Так как на вход синхронизации второго триггера тактовый сигнал поступает через

инвертор, то когда первый триггер находится в режиме хранения, второй триггер пропускает сигнал на выход схемы. И

наоборот, когда первый триггер пропускает сигнал с входа схемы на свой выход, второй триггер находится в режиме

хранения.

![]()

Обратите внимание, что сигнал на выходе всей схемы в целом не зависит от сигнала на входе «D» схемы. Если первый

триггер пропускает сигнал данных со своего входа на выход, то второй триггер в это время находится в режиме хранения

и поддерживает на выходе предыдущее значение сигнала, то есть сигнал на выходе схемы тоже не может измениться.. В результате проведённого анализа временных диаграмм мы определили, что сигнал в схеме, приведенной на рисунке 15

запоминается только в момент изменения сигнала на синхронизирующем входе «C» с единичного потенциала на нулевой.

В результате проведённого анализа временных диаграмм мы определили, что сигнал в схеме, приведенной на рисунке 15

запоминается только в момент изменения сигнала на синхронизирующем входе «C» с единичного потенциала на нулевой.

Динамические D триггеры выпускаются в виде готовых микросхем или входят в виде готовых блоков в составе больших

интегральных схем, таких как базовый матричный кристалл (БМК) или программируемых логических интегральных схем (ПЛИС).

Условно-графическое обозначение D триггера, запоминающего информацию по фронту тактового сигнала,

приведено на рисунке 12.

То, что триггер запоминает входной сигнал по фронту, отображается на условно-графическом обозначении треугольником,

изображённым на выводе входа синхронизации. То, что внутри этого триггера находится два триггера, отображается в среднем

поле условно-графического изображения двойной буквой T.

Иногда при изображении динамического входа указывают, по какому фронту триггер (или триггеры) изменяет своё состояние.

В этом случае используется обозначение входа, как это показано на рисунке 18.

Рисунок 18. Обозначение динамических входов

На рисунке 18 а обозначен динамический вход, работающий по переднему (нарастающему) фронту сигнала. На рисунке 18 б

обозначен динамический вход, работающий по заднему (спадающему) фронту сигнала.

Промышленностью выпускаются готовые микросхемы, содержащие динамические триггеры. В качестве примера можно назвать

микросхему 1533ТМ2. В этой микросхеме содержится сразу два динамических триггера. Они изменяют своё состояние по

переднему фронту сигнала синхронизации.

Дата последнего обновления файла

09.03.2020